Introducción

Comúnmente se expresa que un sistema puede correr satisfactoriamente a 100MHz, o a 133MHz o cualquier otra frecuencia. Qué significa esto? Porqué a esa frecuencia como máxima frecuencia? Quién fija ese límite en un circuito digital? y Cómo se obtiene 6 calcula, ese número? ? Muuuchas preguntas para contestarlas en un simple blog, pero... haré lo que pueda para contestarlas . . . :) .

Periodo Mínimo

En primer lugar recordemos que el periodo de reloj de un sistema es el que 'marca el paso' en el sistema. Si el periodo es largo, el sistema da pasos (entrega resultados/valores) a pasos grandes (sistema lento), si el periodo del reloj es pequeño, el sistema entregará resultados a pasos mas cortos, es decir mas rápidamente.

Recordemos también que la frecuencia de funcionamiento de un sistema es la inversa del periodo de ese mismo sistema: F = 1/T (periodo). Por ello para encontrar la máxima frecuencia debemos encontrar el periodo mínimo . . .

Cómo calcular u obtener el periodo mínimo?

Bien, en un sistema digital el periodo mínimo está compuesto por los retardos MÁXIMOS de los componentes sincrónicos, de los componentes combinacionales , y de las interconecciones entre ellos.

Veamos que significa esto: primero, en un sistema hay muchos caminos sincrónicos (camino de conexión entre flip-flops), pero el que es de interés para el calculo del periodo mínimo es el camino (path) MAS LENTO de todos, es decir el que tiene los retardos MÁXIMOS. El camino mas lento también es llamado camino CRITICO (critical path).

Bien, en un sistema digital el periodo mínimo está compuesto por los retardos MÁXIMOS de los componentes sincrónicos, de los componentes combinacionales , y de las interconecciones entre ellos.

Veamos que significa esto: primero, en un sistema hay muchos caminos sincrónicos (camino de conexión entre flip-flops), pero el que es de interés para el calculo del periodo mínimo es el camino (path) MAS LENTO de todos, es decir el que tiene los retardos MÁXIMOS. El camino mas lento también es llamado camino CRITICO (critical path).

Componentes del periodo mínimo:

- Retardo Sincrónico: cuanto se demora en estar estable el dato a la salida de un flip-flip luego del flanco activo del reloj.

- Retardo combinacional: está compuesto por los componentes no sincrónicos, pueden ser compuertas lógicas, mux, decodificadores, LUTs (en el caso de un FPGA), etc, del camino crítico. Puede haber mas de uno de estos componentes; el retardo de cada uno se suma para lograr el retardo total. La cantidad de componentes combinacionales en el camino critico es normalmente informado en el reporte de frecuencia máxima como 'niveles lógicos' (logic levels). Si se informa que el 'logic level' es 5, significa que en el camino critico hay 5 componentes lógicos combinacionales.

- Retardo de ruteo o de conexiones en el camino critico:

- Entre la salida del componente sincrónico (flip-flop) y la entrada a los componentes combinacionales.

- Entre los componentes combinacionales.

- Entre la salida de los componentes combinacionales y la entrada del flip-flop.

- Tiempo de establecimiento del flip-flop donde termina el camino critico. El dato de entrada tiene que estar un tiempo de establecimiento (dado por la hoja de datos) antes de la llegada del flanco activo del reloj, a fin de evitar problemas de metaestabilidad.

- Margen de periodo: normalmente los valores de los retardos máximos de los puntos anteriores pueden estar afectados por lo que se llama PVT (process, volume, temperature) y los valores dados por la hoja de datos no son los que realmente tenga el circuito en funcionamiento. Por ello se agrega un cierto margen para asegurarse la estabilidad del sistema.

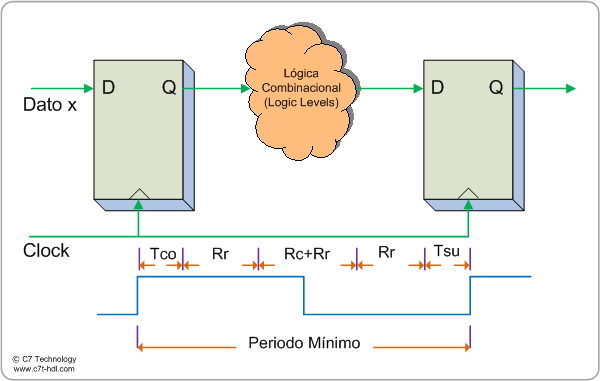

Como bien se dice, una imagen vale mas que mil palabras, la siguiente figura muestra gráficamente lo anteriormente descrito en palabras:

En ésta figura los tiempos detallados son los siguientes:

- Tco: retardo sincrónico, comúnmente llamado 'clock to output'.

- Rr : retardo de ruteo.

- Rc : retardo total de la lógica combinacional, que puede tener varios niveles.

- Tsu: tiempo de establecimiento del flip-flop.

Con todo esto podemos ahora describir la fórmula para calcular el periodo mínimo que nos va dar la frecuencia máxima de funcionamiento del sistema:

Los softwares provistos por los fabricantes de FPGAs ofrecen herramientas que realizan el análisis de todos los caminos sincrónicos del sistema. Estas herramientas realizan lo que se llama un Static Timing Analysis (STA) y reportan el camino más críticos y los siguientes casos no tan críticos. Por ejemplo Altera Quartus provee TimeQuest, Xilinx ISE ofrece Timing Analyzer, Libero de Actel ofrece SmartTime. En un anterior post detallé la información dada por Timing Analyzer.

A modo de ejemplo de la informacion proviste por una herramienta STA, se puede ver a continuación un ejemplo de la información de un camino critico dada por la herramienta TimeQuest de Altera.

Analicemos ésta información: La primer columna muestra los tiempos de ya sea de una celda lógica o de un ruteo. La tercer columna detalla el componente o conexión motivo del retardo: el tiempo referenciado como CELL es el retardo combinacional de la celda lógica detallada en le última columna de la derecha. El tiempo IC se refiere al retardo de ruteo o de interconexión entre las celdas lógicas combinacionales. Como puede verse algunos retardos de IC es igual a 0.000; esto se debe al ruteo dedicado que existe dentro de cada bloque básico del FPGA. El retardo total de este camino mas critico, que es el periodo mínimo al que puede correr satisfactoriamente este sistema, es de 2.331ns. Solo como referencia: La información de la quinta columna detalla el componente lógico usado, y la ultima columna el nombre dado por la herramienta de Place and Route para asociar el componente lógico con el nombre usado en el código VHDL.

Esta información es mas fácil de interpretar viendo el esquemático de éste camino. Tanto Altera, como Actel y Xilinx ofrecen esta vista. He preparado una figura que relaciona todo lo visto hasta acá, asociando el esquemático generado por la herramienta de análisis de tiempo y la figura anteriormente presentada.

Como ya dije al principio este es un cálculo básico del periodo mínimo de un sistema; en un próximo blog trataré de ir mas en detalle teniendo en cuenta por ejemplo el corrimiento del reloj (clock skew), retardos del camino de datos, jitter del reloj, etc....

De todos modos espero que este post haya sido de utilidad (avisen si es así :) .

(version .pdf click acá :) )

(version .pdf click acá :) )